电子照片:

一.基本信息

1.博士

2.联系方式:yliang017@e.ntu.edu.sg

二.个人简介

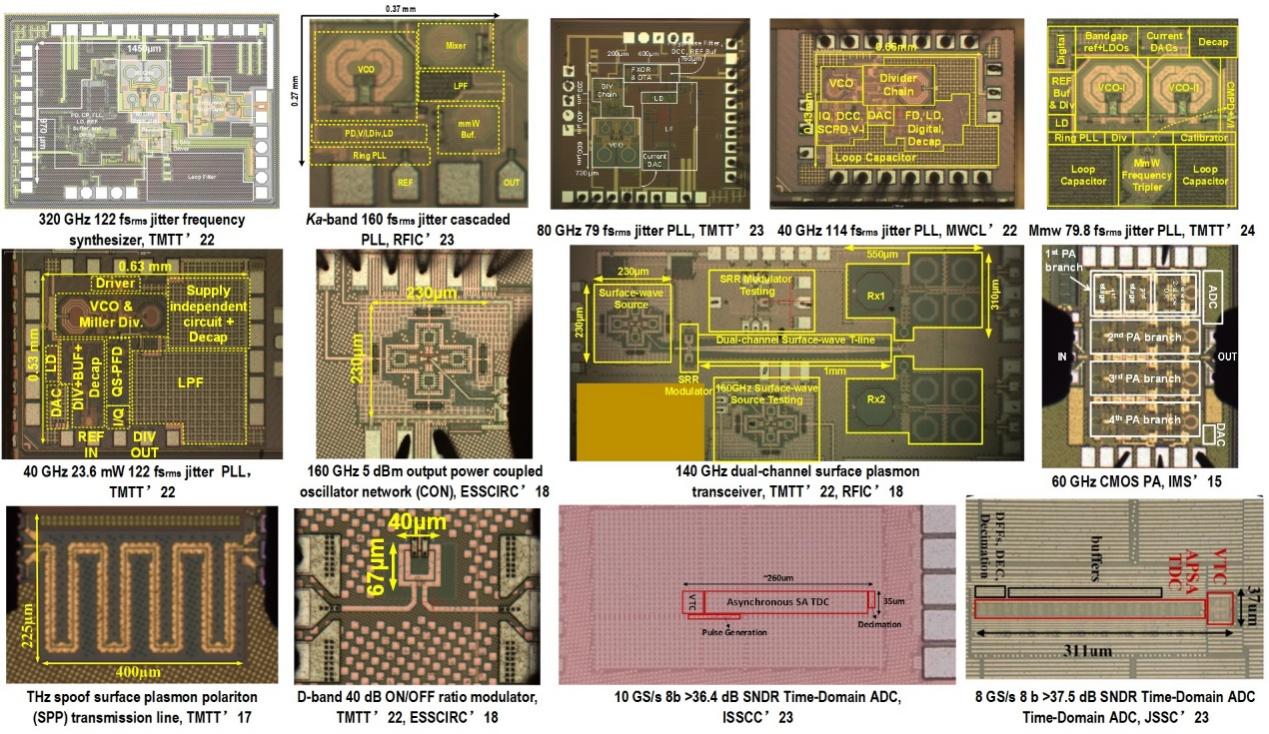

工学博士,毕业于南洋理工大学。主要研究方向包括CMOS/BiCMOS毫米波/太赫兹电路和Time-Domain ADC。

三 .教育经历

2017.01—2022.07 南洋理工大学,博士

2008.09—2012.07 西安电子科技大学,本科

四.职业经历

2023至今 广州大学 教师

2018.2-2020.12 德国高性能微电子研究院(IHP)实习

2013-2016 南洋理工大学 科研助理

五.讲授课程

模拟电子技术II,数字集成电路设计,射频集成电路设计,CMOS高速集成电路设计

六.研究成果

近期发表的期刊论文

[1] Y. Liang et al., "A 28.8−43.2 GHz 79.8 fsrms Jitter and −78.5 dBc Reference Spur PLL Exploiting Complementary Mixing Phase Detector with Mismatch Calibration," IEEE Trans. Microw. Theory Techn., accepted, 2024, DOI: 10.1109/TMTT.2024.3363465.

[2] Y. Liang et al., "Spur Canceling Technique by Folded XOR Gate Phase Detector and Its Application to a Millimeter-Wave SiGe BiCMOS PLL," IEEE Trans. Microw. Theory Techn., Vol. 71, No. 8, pp. 3572–3584, 2023.

[3] Y. Liang et al, "A 40 GHz CMOS PLL With −75-dBc Reference Spur and 121.9-fsrms Jitter Featuring a Quadrature Sampling Phase-Frequency Detector," IEEE Trans. Microw. Theory Techn., Vol. 70, No. 4, pp. 2299–2314, Feb. 2022.

[4] Y. Liang et al., "A Low-Jitter and Low-Reference-Spur 320 GHz Signal Source With an 80 GHz Integer-Ν Phase-Locked Loop Using a Quadrature XOR Technique," IEEE Trans. Microw. Theory Techn, Vol. 70, No. 5, pp. 2642–2657, May 2022.

[5] Y. Liang, et al., "A 13.5 Gb/s 140-GHz Silicon Redriver Exploiting Metadevices for Short-Range OOK Communications," IEEE Trans. Microw. Theory Techn., Vol. 70, No. 1, pp. 239–253, Jan. 2022.

[6] Q. Chen, Y. Liang (equally credited first author), et al., "A Single-Channel 10GS/s 8b >36.4dB SNDR Time-Domain ADC Featuring Loop-Unrolled Asynchronous Successive Approximation in 28nm CMOS,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2023, 2023, pp. 278–280.

[7] Y. Liang, et al., "An Energy-efficient Sub-THz I/O by Surface Plasmonic Polariton Interconnect in CMOS," IEEE Trans. Microw. Theory Techn., Vol. 65, No. 8, pp. 2762–2774, Mar. 2017.