近日,电子与通信工程学院曾衍瀚副教授团队在工艺、电压和温度(PVT)扰动下的模拟集成电路优化方面取得重要研究进展,首次报道了基于多任务进化的集成电路PVT鲁棒性优化的工作,建立了PVT知识迁移框架,提出了基于直流工作点的PVT分析模型,有效减少了负面的知识迁移。相关研究成果分别发表在电子设计自动化(EDA)领域国际四大顶会之一的2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD)和集成电路领域国际顶级期刊IEEE Transactions on Circuits and Systems I: Regular Papers。

01丨研究背景

尽管电子设计自动化(EDA)技术至今已经取得了显著进展,模拟集成电路(IC)的设计过程仍主要依赖于手工进行精确计算和对晶体管尺寸的多次调整。模拟电路固有的高度非线性特性使得这一设计过程既低效又可能达不到最优。此外,设计的结果往往缺乏确定性,且极度依赖于设计者的个人经验和专业知识。尤其是,由于工艺、电压和温度(PVT)的变化,性能的偏差在自动化设计中的应对措施尚未得到充分的解决。因此,发展模拟EDA技术,确保其能在面对PVT变化时保持设计的稳健性和最优性,成为一个迫切需要解决的问题。

02丨研究内容

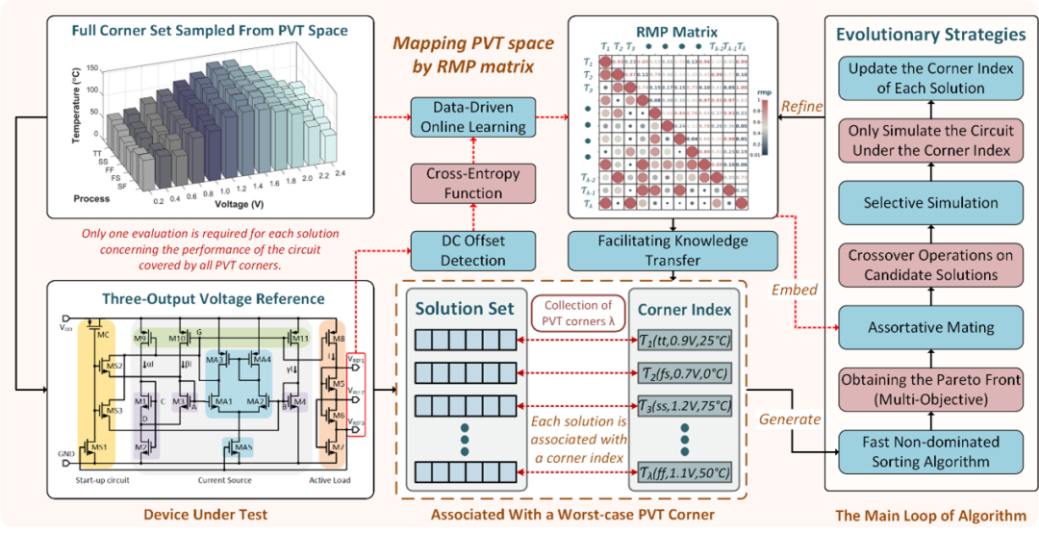

基于此,曾衍瀚副教授团队为了应对模拟集成电路设计中因PVT变化带来的挑战,提出了一种PVT迁移框架。本框架通过将PVT变化视为一系列需要进行知识迁移的优化任务,旨在提升设计的PVT稳健性。该框架通过促进所有变体间的知识共享,显著提高了设计的效率,并有效减少了在每次模拟过程中对变体进行评估的次数。

为确保知识迁移的效率和稳健性,团队研究构建了一种新型策略,即在优化过程中监测直流工作点偏移情况,并建立“角点模型”来探索PVT变化的内在规律。这种方法有助于减轻负面知识转移的影响,进而确保在面对PVT变化时能够实现更加准确和可靠的模拟IC设计。该框架的性能优于现有方法,在减少60%仿真次数的情况下,将目标芯片电路功耗降低了60%,温度特性提高80%。

EDA行业具有“芯片之母”的地位,贯穿半导体产业链各个环节,是半导体“卡脖子”关键环节。团队将与国产EDA龙头企业广州市概伦电子进一步合作,与概伦电子的NanoDesigner协同,打通模拟集成电路IP自动化设计全流程,为实现高性能化,高集成度、高灵活性的模拟集成电路设计提供新的解决方案,从点到链突破,助力国产EDA加速突围。

基于多任务进化的PVT知识迁移架构

03丨研究相关

曾衍瀚副教授和电子科技大学李耘教授为论文的通讯作者,硕士生李锦韬为论文的第一作者,广州大学为论文第一通讯单位。该研究工作得到了国家自然科学基金、广东省自然科学基金和广州市科技计划(市校联合)等项目的支持。通讯作者曾衍瀚副教授,现任IEEE高级会员,CCF高级会员,现任广州大学电子与通信工程学院副院长,IEEE固态电子电路学会广州分会副主席,主要致力于模拟/混合信号集成电路设计及其自动化的研究与应用。

论文链接:

https://ieeexplore.ieee.org/document/10323899

https://ieeexplore.ieee.org/document/10362966